# Automating the Design of Programmable Interconnect for Reconfigurable Architectures

Stefan Nikolić

EPFL, 14.12.2023

École Polytechnique Fédérale de Lausanne

## **Custom Hardware Is Our Reality**

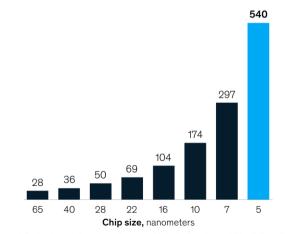

## But What If We Don't Have \$0.5B?

Chip-design cost,<sup>1</sup> \$ million

Source: H. Bauer et al. Semiconductor design and manufacturing: Achieving leading-edge capabilities. McKinsey & Company, 2020

# It's All Like a Movie

#### Professional cinematography is expensive

Sven Nykvist and Andrei Tarkovsky, 1986

Average feature film budget: \$100-150 million (https://www.nfi.edu/how-much-does-it-cost-to-make-a-movie/)

## It's All Like a Movie

#### But a DIY shot of your dog playing might be more valuable

# How to Capture Incredible Pet Photos and Videos With the Galaxy Note20

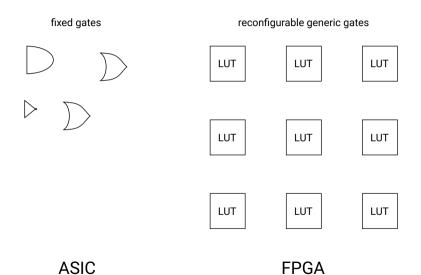

### FPGA: The Cell-Phone Camera of Custom Hardware

BY IEEE SPECTRUM | 30 JUN 2017 | 1 MIN READ |

## FPGA: The Cell-Phone Camera of Custom Hardware

## FPGA: The Cell-Phone Camera of Custom Hardware

fixed interconnect programmable interconnect LUT LUT LUT prefabricated wire programmable switch LUT LUT LUT switch block LUT LUT LUT

#### Cameras Got Better Over Time

Pentax \*ist D Year: 2003 Price (inflation adjusted): \$2500 (body only) Google Pixel 8 Year: 2023 Price: \$700

#### And So Did FPGAs

#### INVITED PAPER

#### Three Ages of FPGAs: A Retrospective on the First Thirty Years of FPGA Technology

This paper reflects on how Moore's Law has driven the design of FPGAs through three epochs: the age of invention, the age of expansion, and the age of accumulation. By STEPHEN M. (STEP) TELEMERGER. Fellow IEE

nology in the early 1990s. As a result, FPGAs began the Age of Expansion lagging the process introduction curve. In the 1990s, they became process leaders as the foundries realized the value of using the FPGA as a process-driver application. Foundries were able to build SRAM FPGAs as soon as they were able to yield transistors and wires in a new technology. FPGA vendors sold their huge devices while foundries refined their processes. Each new generation of silicon

# For two decades, FPGAs were fabrication technology drivers, first to profit from Moore's law

# The "Let Moore Do It" Era of Programmable Interconnect Design

#### Architectural Enhancements in Stratix V<sup>™</sup>

David Lewis\*, David Cashman\*, Mark Chan, Jeffery Chromczak\*, Gary Lai, Andy Lee, Tim Vanderhoek\*, Haiming Yu Altera Corporation, 150 Bior St W., Suite 400, Toronto, Ont., Canada MS2 X29 (idevise,Gashman,rchan, Jarkimmorz, gal, alek randern, hyv) @latera.com Although relatively small, the modularity results in a desire to accommodate a moderate increase in routing demand with adjustments to wire length, rather than the <u>coarser auantization of</u> increasing columns of routing multiplexers. <u>Consequently rather</u> than completely re-architect the routing, we explored minor variations that could keep pace with the increase in routing demand as well as obtain performance improvement.

#### Rule 2: Rely on intuition

Trimberger: So we just flow through that, and It actually made a tot of really good decisions because we had a tot of people with expertise at that point, which we didn't have five years earlier because there just wasn't that much expertise in the FPGA busices.

**Oral History of Steve Trimberger**

Interviewed by: Doug Fairbairn Jesse Jenkins

CHM Ref: X8370.2018

© 2017 Computer History Museum

Page 33 of 60

#### The End of an Era

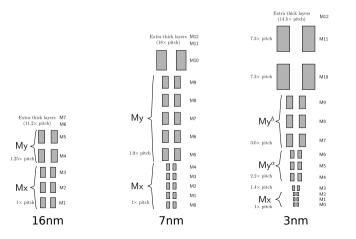

#### Wire scaling has become problematic

## The End of an Era

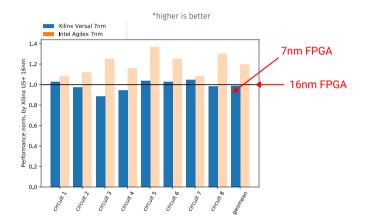

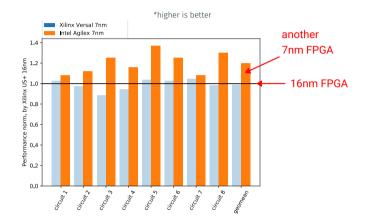

Source: Z. Weng and K. Tondehal. Performance Advantages on OpenCores with Intel Agilex® 7 FPGAs. Intel White Paper 787066, 2023

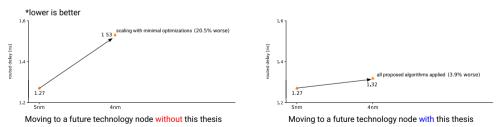

Scaling no longer makes FPGAs faster

## The End of an Era

Source: Z. Weng and K. Tondehal. Performance Advantages on OpenCores with Intel Agilex® 7 FPGAs. Intel White Paper 787066, 2023

But how did Agilex get it better?

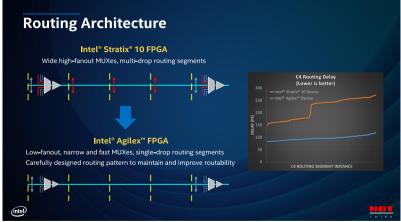

# How Did Agilex Get It Better?

Source: I. Ganusov, M. Iyer, N. Cheng, A. Meisler. Agilex<sup>™</sup> Generation of Intel® FPGAs. Hot Chips 2020

#### By drastically redesigning the programmable interconnect architecture

#### And What Was the Cost?

IEEE Spectrum / TSMC's 5-Nanometer Process on Track for First... Q Type to search

TSMC's 5-Nanometer Process on Track for First Half of 2020 >Devices are 15 percent faster, 30 percent more energy efficient

BY SAMUEL K. MOORE | 13 DEC 2019 | 2 MIN READ |

FPGAs now lag behind the latest technology by two full nodes

# Can't We Design Programmable Interconnect More Quickly?

# Yes, by design automation

- Critical paths unknown at fabrication time (before each user circuit is programmed)

- $\implies$  need to optimize for the typical case

- $\implies$  inherently empirical

2. Huge design spaces

# So can we automate programmable interconnect design?

#### Yes We Can!

This thesis introduced several new algorithms that showed this possible.

Dr. Grace Zgheib

Prof. Dr. Francky Catthoor

Dr. Zsolt Tőkei

THANK YOU

Dr. Mirjana Stojilović

Mr. Morten B. Petersen